當(dāng)前位置:廣州虹科電子科技有限公司>>技術(shù)文章>>自動駕駛 HIL 測試:構(gòu)建 “以假亂真“ 的實(shí)時數(shù)據(jù)注入系統(tǒng)

自動駕駛 HIL 測試:構(gòu)建 “以假亂真“ 的實(shí)時數(shù)據(jù)注入系統(tǒng)

01 引言

在端到端自動駕駛的研發(fā)競賽中,算法的迭代速度遠(yuǎn)超物理世界的測試能力。單純依賴路測不僅成本高昂、周期漫長,更無法窮盡決定系統(tǒng)安全性的關(guān)鍵邊緣場景(Corner Cases)。

因此,硬件在環(huán)(HIL)仿真測試成為出路。然而,將仿真數(shù)據(jù)閉環(huán)注入域控制器流程中存在諸多技術(shù)難度,特別是高像素相機(jī)原始數(shù)據(jù),如何無損、無延遲地將數(shù)據(jù)灌入對時序和信號要求極為苛刻的域控制器中成為了當(dāng)前調(diào)試HiL系統(tǒng)的主要挑戰(zhàn)!

本文將解析如何構(gòu)建一套真正讓車載控制器“信以為真"的注入系統(tǒng)。通過DMA/RDAM技術(shù)實(shí)現(xiàn)“零拷貝"數(shù)據(jù)路徑,從根源上消除傳輸延遲。同精確控制 CSI-2/GMSL2 協(xié)議棧,確保信號的物理層保真度。并運(yùn)用 I2C 作為控制與調(diào)試的“生命線",確保復(fù)雜鏈路的穩(wěn)定建立與監(jiān)控。

02 系統(tǒng)架構(gòu)概覽

高保真實(shí)時仿真注入系統(tǒng)的核心目標(biāo),是將仿真環(huán)境中生成的傳感器數(shù)據(jù),以極低的延遲和與真實(shí)傳感器別無二致的物理信號特性,注入到待測的設(shè)備(DUT)中。這套系統(tǒng)的典型架構(gòu)由三個關(guān)鍵部分組成:仿真主機(jī)(Simulation Host)、數(shù)據(jù)注入設(shè)備(Injection Device)和待測設(shè)備(DUT, Device Under Test)。

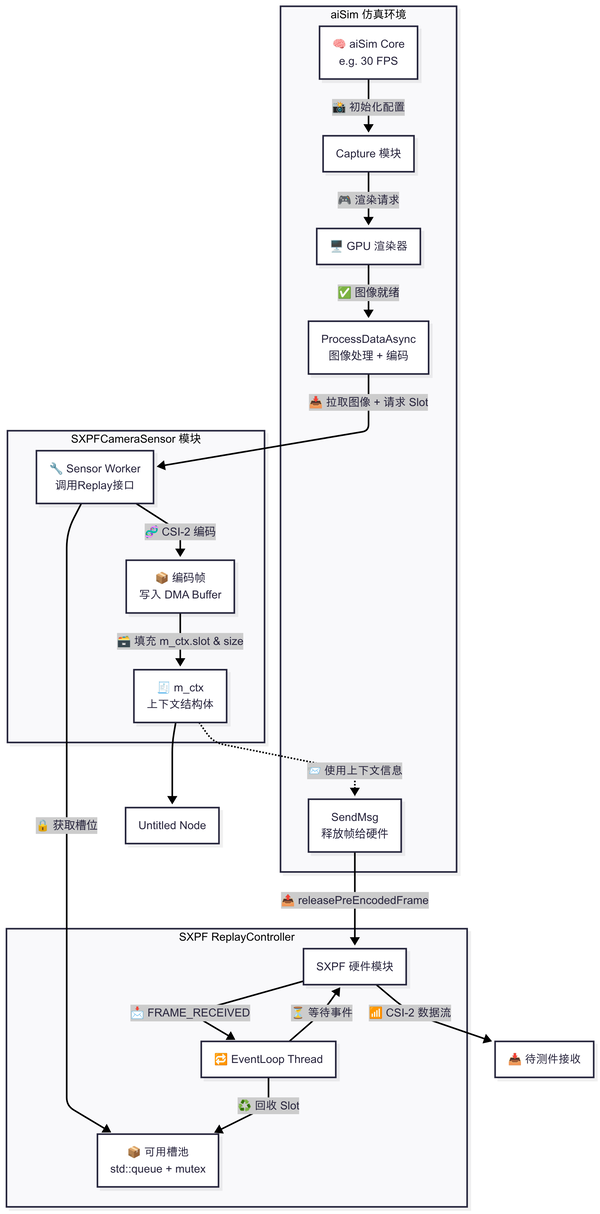

數(shù)據(jù)流的完整流程如下:

(1)數(shù)據(jù)生成:仿真軟件aiSim在仿真主機(jī)上根據(jù)預(yù)設(shè)場景生成相機(jī)的原始圖像幀數(shù)據(jù);

(2)數(shù)據(jù)傳輸:這些原始數(shù)據(jù)通過網(wǎng)絡(luò)被發(fā)送到數(shù)據(jù)注入設(shè)備;

(3)數(shù)據(jù)處理與編碼:注入設(shè)備上的應(yīng)用程序(如camera_sensor.cpp中的邏輯)接收數(shù)據(jù)。為了實(shí)現(xiàn)低延遲,數(shù)據(jù)被直接送入一塊專用的硬件板卡(proFRAME);

(4)DMA/RDMA傳輸:數(shù)據(jù)通過PCIe總線,利用直接內(nèi)存訪問(DMA)或遠(yuǎn)程直接內(nèi)存訪問(RDMA)技術(shù),被高效地傳輸?shù)阶⑷氚蹇ǖ膬?nèi)存或板載GPU內(nèi)存中,此過程最大限度地減少了CPU的干預(yù);

(5)CSI-2/GMSL2封裝:板卡上的FPGA或?qū)S锰幚砥鳎ˋSIC)將內(nèi)存中的圖像數(shù)據(jù)打包成CSI-2協(xié)議格式,并驅(qū)動GMSL2序列化器(Serializer)芯片將其轉(zhuǎn)換為高速串行信號;

(6)物理注入:GMSL2信號通過同軸電纜傳輸?shù)紻UT的GMSL2解串器(Deserializer),DUT的處理器(SoC)通過其CSI-2接口接收到圖像數(shù)據(jù),就像從一個真實(shí)的相機(jī)接收一樣。

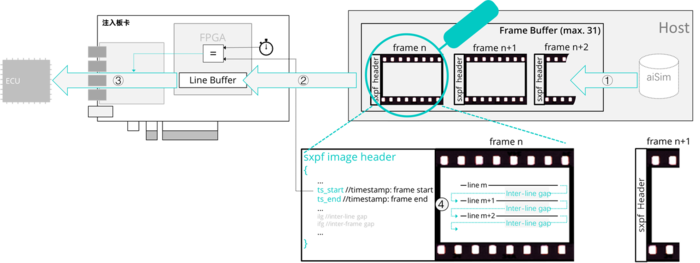

① 仿真主機(jī)aiSim高保真相機(jī)數(shù)據(jù)傳輸?shù)綆彌_區(qū)(DMA);

② 逐行傳輸?shù)絧roFRAME硬件(PCIe);

③ 基于時間戳/行間隙的時鐘周期數(shù)發(fā)送圖像幀(CSI-2幀);

④ 基于行間隙定義圖像幀行間時序。

03 技術(shù)深度解析

1、仿真源數(shù)據(jù)與準(zhǔn)備

仿真注入的起點(diǎn)是仿真軟件生成的源數(shù)據(jù)。在我們的案例中,仿真軟件aiSim輸出的是原始的相機(jī)圖像幀(RAW12)。這些數(shù)據(jù)在注入前,必須經(jīng)過精心的預(yù)處理,以確保DUT能夠正確解析。

核心的預(yù)處理步驟是在Host端完成的。這個過程并非簡單的格式轉(zhuǎn)換,而是嚴(yán)格按照待測件的需求,將aiSim生成的裸數(shù)據(jù)(payload)封裝成一個完整的、符合物理層規(guī)范的數(shù)據(jù)包。具體來說:

(1)數(shù)據(jù)拷貝:將aiSim生成的圖像數(shù)據(jù)src_image.m_data拷貝到一個臨時的暫存緩沖區(qū)staging_buffer中;

(2)CSI-2編碼:調(diào)用核心編碼函數(shù)csi2_single_encode,將暫存區(qū)中的裸數(shù)據(jù)打包成CSI-2格式。這一步會根據(jù)配置添加CSI-2的包頭(Packet Header)、數(shù)據(jù)負(fù)載(Data Payload)、錯誤校驗(yàn)碼(ECC)等;

(3)proFRAME頭部填充:在編碼后的CSI-2數(shù)據(jù)包前,附加一個sxpf_image_header_t頭部。這個頭部包含了注入任務(wù)所需的關(guān)鍵元數(shù)據(jù),例如圖像的寬、高、每像素位數(shù)(bpp)、時間戳,以及兩個至關(guān)重要的時序參數(shù):ilg (Image Line Gap) 和 ifg (Image Frame Gap);

ilg:行間隙,定義了上一行圖像數(shù)據(jù)傳輸完成到下一行開始之間的精確時間間隔。

ifg:幀間隙,定義了上一幀圖像數(shù)據(jù)傳輸完成到下一幀開始之間的精確時間間隔。

這兩個參數(shù)直接控制了數(shù)據(jù)在GMSL2鏈路上的“微觀時序"。如果設(shè)置不當(dāng),即使數(shù)據(jù)內(nèi)容正確,DUT的解串器也可能因?yàn)椴环项A(yù)期的時序而無法鎖定信號或正確接收數(shù)據(jù),導(dǎo)致回放幀率異常波動甚至鏈路失敗。

2、零拷貝與低延遲的基石:DMA與RDMA

要實(shí)現(xiàn)“實(shí)時"注入,數(shù)據(jù)在注入設(shè)備內(nèi)部的搬運(yùn)效率至關(guān)重要。DMA和RDMA正是解決此問題的關(guān)鍵。

DMA (Direct Memory Access):DMA是現(xiàn)代計(jì)算機(jī)系統(tǒng)的基本特性。它允許外設(shè)(如proFRAME板卡)在沒有CPU干預(yù)的情況下,直接與主內(nèi)存進(jìn)行數(shù)據(jù)讀寫。在默認(rèn)的注入流程中,proFRAME從相機(jī)或網(wǎng)絡(luò)獲取數(shù)據(jù)后,通過PCIe總線直接將數(shù)據(jù)寫入由CPU預(yù)先分配好的內(nèi)存緩沖區(qū)(Buffer)。這避免了CPU逐字節(jié)拷貝數(shù)據(jù)的開銷,顯著提升了吞吐量。通常,基于DMA的PCIe Gen3 x8鏈路,可以將延遲控制在1毫秒級別。

NVIDIA GPUDirect RDMA:GPUDirect RDMA允許將仿真的圖像數(shù)據(jù)直接從NVIDIA GPU發(fā)送到proFrame中,無需占用主系統(tǒng)內(nèi)存(RAM)的帶寬,也無需CPU進(jìn)行任何數(shù)據(jù)中轉(zhuǎn)。整個數(shù)據(jù)鏈路變?yōu)椋篴iSim -> GPU顯存 -> PCIe -> proFRAME 。這消除了內(nèi)存與顯存之間的拷貝開銷,也為CPU節(jié)約了寶貴的內(nèi)存帶寬資源,是構(gòu)建微秒級延遲注入系統(tǒng)的核心技術(shù)。

3、物理鏈路注入:GMSL2與CSI-2協(xié)議棧

GMSL2 (Gigabit Multimedia Serial Link 2):作為物理層載體,是專為汽車應(yīng)用設(shè)計(jì)的高速串行接口。在仿真注入中,它的角色就是將編碼好的數(shù)字圖像信號,轉(zhuǎn)換為能在物理線纜上傳輸?shù)碾娦盘枴?/p>

CSI-2 (Camera Serial Interface 2):CSI-2是在GMSL2之上傳輸?shù)?strong style="font-weight: bold !important;">數(shù)據(jù)協(xié)議。它定義了數(shù)據(jù)如何被組織和打包。

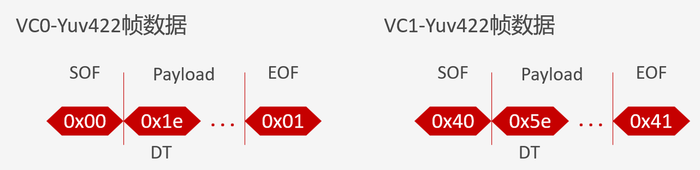

(1)數(shù)據(jù)包結(jié)構(gòu)

一個CSI-2數(shù)據(jù)包通常由幀起始符(SOF - Start of Frame)、包頭(Packet Header)、數(shù)據(jù)負(fù)載(Payload)和幀結(jié)束符(EOF - End of Frame)組成。如資料所示,SOF和EOF的值可以用來區(qū)分不同的虛擬通道(Virtual Channel, VC)。例如,VC0的SOF/EOF值為0x00/0x01,而VC1則為0x40/0x41。

(2)實(shí)現(xiàn)關(guān)鍵

整個注入鏈路的最后一公里,就是將內(nèi)存中(通過DMA/RDMA獲取)準(zhǔn)備好的、包含sxpf_image_header_t和CSI-2編碼后負(fù)載的完整數(shù)據(jù)幀,交給proFRAME板卡。板卡上的邏輯會解析這些數(shù)據(jù),驅(qū)動GMSL2序列化器芯片,嚴(yán)格按照ilg和ifg定義的時序,將CSI-2數(shù)據(jù)包序列化后發(fā)送出去,即通過sxpf_release_frame()函數(shù)將準(zhǔn)備好的數(shù)據(jù)緩沖區(qū)slot句柄和數(shù)據(jù)大小交給硬件,硬件隨后便接管了發(fā)送任務(wù)。

04 I2C調(diào)試與驗(yàn)證

在GMSL2鏈路中,I2C是配置和調(diào)試必要的生命線。它負(fù)責(zé)在主機(jī)(proFRAME)和遠(yuǎn)端設(shè)備(DUT)的SerDes(Serializer/Deserializer)芯片之間建立一條雙向控制通道。

1、調(diào)試實(shí)踐

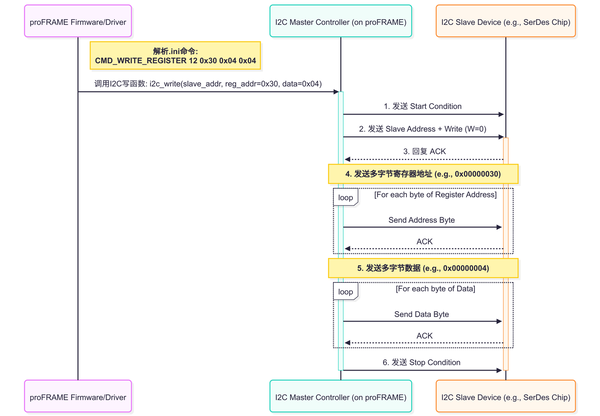

調(diào)試GMSL2鏈路問題時,I2C是最直接的突破口。proFRAME提供的初始化序列文件(.ini文件)就是I2C調(diào)試實(shí)踐的范例。

上述序列圖直觀地展示了.ini文件中的一條高級命令到底層I2C總線時序的完整轉(zhuǎn)換過程。

(1)解析與調(diào)用:proFRAME的固件或驅(qū)動作為控制大腦,首先解析.ini文件中的CMD_WRITE_REGISTER命令,并提取出目標(biāo)從設(shè)備地址、寄存器地址和要寫入的數(shù)據(jù);

(2)啟動通信:固件調(diào)用板載的I2C主控制器,發(fā)起一次寫操作。控制器首先發(fā)送“起始信號",并在總線上廣播目標(biāo)從設(shè)備的地址及寫操作位;

(3)地址與數(shù)據(jù)傳輸:在收到從設(shè)備的“應(yīng)答信號"(ACK)確認(rèn)設(shè)備存在后,主控制器嚴(yán)格按照順序,逐字節(jié)地發(fā)送多字節(jié)的寄存器地址和數(shù)據(jù)。每一次字節(jié)傳輸完成后,都會等待從設(shè)備的ACK,以確保數(shù)據(jù)被成功接收;

(4)結(jié)束通信:所有數(shù)據(jù)發(fā)送完畢后,主控制器發(fā)送“停止信號",釋放I2C總線,完成本次操作。

05 實(shí)踐中的挑戰(zhàn)與考量

在搭建和運(yùn)行一套高保真實(shí)時注入系統(tǒng)的過程中,會遇到諸多工程挑戰(zhàn)

(1)時鐘同步與時序精準(zhǔn):嚴(yán)格來說,仿真主機(jī)、注入設(shè)備和DUT工作在各自的時鐘域下。雖然物理層時鐘可以由GMSL2鏈路恢復(fù),但數(shù)據(jù)流的宏觀時序必須嚴(yán)格受控。正如前述,ilg和ifg參數(shù)的精確計(jì)算和配置至關(guān)重要。需要通過工具分析目標(biāo)相機(jī)真實(shí)的數(shù)據(jù)流特性,或通過專用計(jì)算表格,調(diào)整這些參數(shù),使得注入設(shè)備輸出的數(shù)據(jù)速率(Data Lane Rate)與DUT的期望值精確匹配,從而確保時序上的“保真"

(2)帶寬瓶頸分析:整條鏈路的有效帶寬受限于最慢的一環(huán)。

-仿真?zhèn)龋?/strong>仿真主機(jī)的渲染能力和網(wǎng)絡(luò)出口帶寬;

-注入設(shè)備:PCIe總線帶寬(例如,x8 Gen3理論值為~7.8 GB/s)、DMA/RDMA的實(shí)際效率、CPU到GPU的拷貝速度(在使用DMA時);

-物理鏈路:GMSL2本身的帶寬上限。

在設(shè)計(jì)方案時,必須對每個環(huán)節(jié)的帶寬進(jìn)行評估,確保沒有明顯的瓶頸。例如,即使GMSL2帶寬足夠,但如果采用DMA方式且CPU到GPU的拷貝速度跟不上,同樣會造成幀率下降和延遲增加。

系統(tǒng)穩(wěn)定性:硬件在環(huán)測試通常需要長時間(數(shù)小時甚至數(shù)天)連續(xù)運(yùn)行。

-內(nèi)存管理:必須杜絕內(nèi)存泄漏。在上層實(shí)現(xiàn)中,通過一個固定大小的緩沖區(qū)池(m_availableSlots隊(duì)列)和嚴(yán)謹(jǐn)?shù)纳暾?acquirePlaybackSlot)釋放(releasePreEncodedFrame)邏輯來循環(huán)使用內(nèi)存。當(dāng)硬件處理完一幀數(shù)據(jù)后,會通過事件(SXPF_EVENT_FRAME_RECEIVED)通知上層軟件,軟件再將被釋放的緩沖區(qū)重新加入可用隊(duì)列。這種機(jī)制保證了內(nèi)存使用量的恒定。

-CPU/GPU資源:要避免CPU的忙等待。在acquirePlaybackSlot的實(shí)現(xiàn)中,當(dāng)沒有可用緩沖區(qū)時,線程會進(jìn)行短暫休眠(sleep_for),而不是持續(xù)空轉(zhuǎn),這降低了CPU占用率。

06 總結(jié)

一套成功的高保真實(shí)時仿真注入系統(tǒng),本質(zhì)上是一個解決了計(jì)算、傳輸和物理接口三大領(lǐng)域深度集成問題的系統(tǒng)工程。

通過將DMA/RDMA的零拷貝能力、GMSL2 的高帶寬物理層以及 I2C 的精確控制能力有機(jī)結(jié)合,可以有效攻克傳統(tǒng)HIL測試中存在的帶寬、延遲和保真度瓶頸,從而在實(shí)驗(yàn)室環(huán)境中構(gòu)建起連接虛擬仿真與物理ECU的堅(jiān)實(shí)橋梁。這套技術(shù)棧,是加速自動駕駛算法迭代和保障其功能安全的關(guān)鍵賦能技術(shù)。

6

6